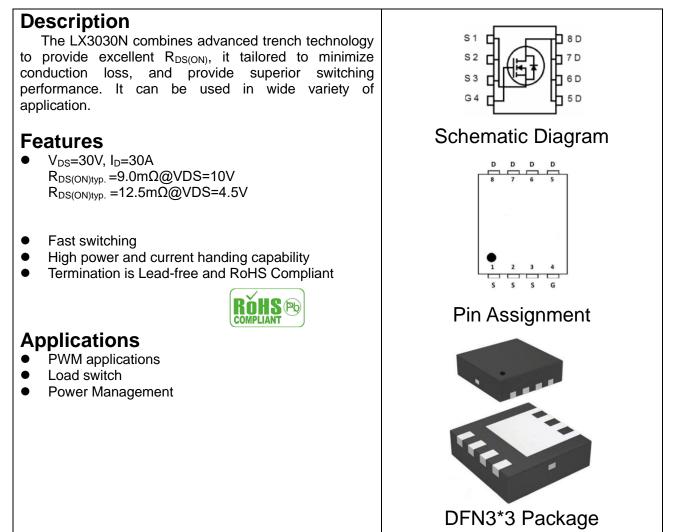

# **CHIPLINK N-Channel Enhancement Mode Power MOSFET**

# Maximum Ratings(T<sub>A</sub>=25°C unless otherwise noted)

| Parameter                              | Symbol                                | Maximum    | Units |

|----------------------------------------|---------------------------------------|------------|-------|

| Drain-Source Voltage                   | V <sub>DS</sub>                       | 30         | V     |

| Gate-Source Voltage                    | V <sub>GS</sub>                       | ±20        | V     |

| Continuous Drain Current               | I <sub>D</sub> (T <sub>C</sub> =25℃)  | 30         | A     |

|                                        | I <sub>D</sub> (T <sub>C</sub> =100℃) | 20         |       |

| Pulsed Drain Current <sup>B</sup>      | I <sub>DM</sub>                       | 120        | A     |

| Maximum Power Dissipation <sup>A</sup> | PD                                    | 9          | W     |

| Single pulse avalanche energy          | E <sub>AS</sub>                       | 36         | mJ    |

| Junction and Storage Temperature Range | T <sub>J</sub> , T <sub>STG</sub>     | -55 To 150 | °C    |

# Thermal Characteristic

| I nermal Resistance, Junction to Case R <sub>QJA</sub> 6.5 C/W | Thermal Resistance, Junction to Case | R <sub>QJA</sub> | 6.5 | °C/W |

|----------------------------------------------------------------|--------------------------------------|------------------|-----|------|

|----------------------------------------------------------------|--------------------------------------|------------------|-----|------|

### **Electrical Characteristics** (T<sub>A</sub>=25°C unless otherwise specified)

| Parameter                          | Symbol              | Test conditions                                       | MIN | TYP  | MAX  | UNIT |

|------------------------------------|---------------------|-------------------------------------------------------|-----|------|------|------|

| Drain-Source Breakdown<br>Voltage  | BV <sub>DSS</sub>   | $V_{GS}$ =0V, I <sub>D</sub> =250uA                   | 30  |      |      | V    |

| Gate-Threshold Voltage             | V <sub>th(GS)</sub> | $V_{DS}=V_{GS}$ , $I_{D}=250$ uA                      |     | 1.5  | 2.2  | V    |

| Gate-body Leakage                  | IGSS                | $V_{DS}=0V, V_{GS}=\pm 12V$                           |     |      | ±100 | nA   |

| Zero Gate Voltage Drain<br>Current | IDSS                | V <sub>DS</sub> =30V, V <sub>GS</sub> =0V             |     |      | 1    | uA   |

| Drain-Source On-Resistance         | D                   | V <sub>GS</sub> =10V, I <sub>D</sub> =5A              |     | 9    | 13   | mΩ   |

| Dialit-Source Off-Resistance       | R <sub>DS(ON)</sub> | V <sub>GS</sub> =4.5V, I <sub>D</sub> =4A             |     | 12.5 | 17   | mΩ   |

| Forward Transconductance           | <b>g</b> fs         | $V_{DS}$ =5V, $I_{D}$ =5A                             | 10  |      |      | S    |

| Dynamic Characteristics            |                     |                                                       |     |      |      |      |

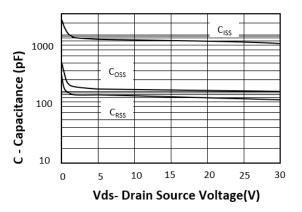

| Input Capacitance                  | Ciss                |                                                       |     | 865  |      | pF   |

| Output Capacitance                 | Coss                | V <sub>DS</sub> = 15V, V <sub>GS</sub> =0V,<br>F=1MHz |     | 105  |      |      |

| Reverse Transfer Capacitance       | C <sub>rss</sub>    |                                                       |     | 86   |      |      |

| Switching Capacitance              |                     |                                                       |     |      |      |      |

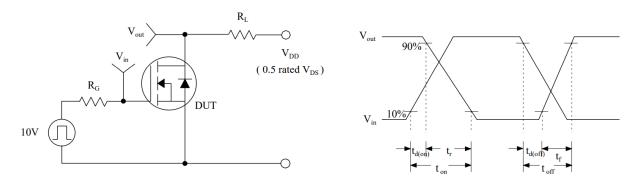

| Turn-on Delay Time                 | t <sub>d(on)</sub>  |                                                       |     | 5    |      | nS   |

| Turn-on Rise Time                  | tr                  | $V_{DD}$ = 15V, R <sub>L</sub> =3 $\Omega$            |     | 4    |      | nS   |

| Turn-off Delay Time                | t <sub>d(off)</sub> | $V_{GS} = 10V, R_{GEN} = 3\Omega$                     |     | 22   |      | nS   |

| Turn-off Fall Time                 | t <sub>f</sub>      |                                                       |     | 6    |      | nS   |

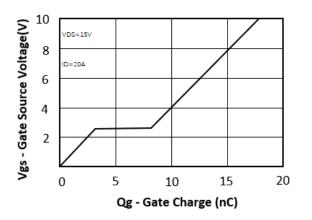

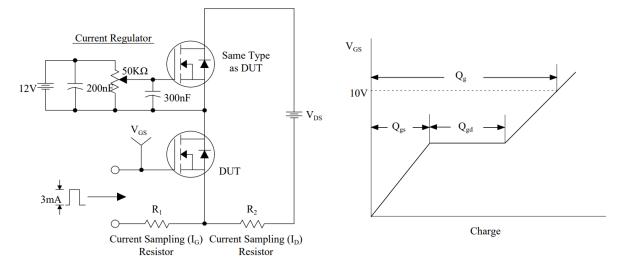

| Total Gate Charge                  | Qg                  | V <sub>DS</sub> = 15V, I <sub>D</sub> =5A,            |     | 18   |      | nC   |

| Gate-Source Charge                 | Q <sub>gs</sub>     | V <sub>GS</sub> =4.5V                                 |     | 3    |      | nC   |

| Gate-Drain Charge                  | Q <sub>gd</sub>     |                                                       |     | 5    |      | nC   |

| Drain-Source Diode Characteristics |                     |                                                       |     |      |      |      |

| Diode Forward Voltage              | V <sub>SD</sub>     | V <sub>GS</sub> =0V, I <sub>D</sub> =5A               |     |      | 1.2  | V    |

| Diode Forward Current              | ls                  |                                                       |     |      | 30   | А    |

#### Notes:

- A. The Power dissipation  $P_D$  is based on  $T_{J(MAX)}{=}150~{}^\circ\!{\rm C}$  , using<10s junction-to ambient thermal resistance.

- B. Repetitive rating, pulse width limited by junction temperature  $T_{J(MAX)}=150$  °C.Ratings are based on low frequency and duty cycles to keep initial  $T_{J}=25$  °C.

- C. The Static characteristics in Figures are obtained using  $<300 \ \mu$  s pulses, duty cycle 2% max.

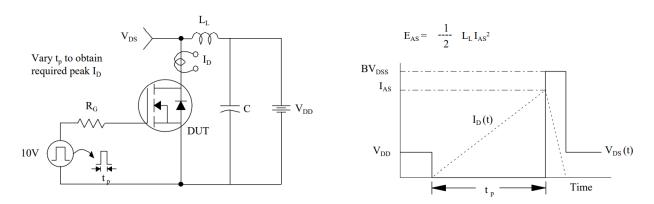

- D. EAS condition: TJ=25  $^\circ C$  ,V\_DD=15V, V\_GS=10V, R\_G=25\Omega, L=0.5Mh, I\_{AS}=19A\_\circ

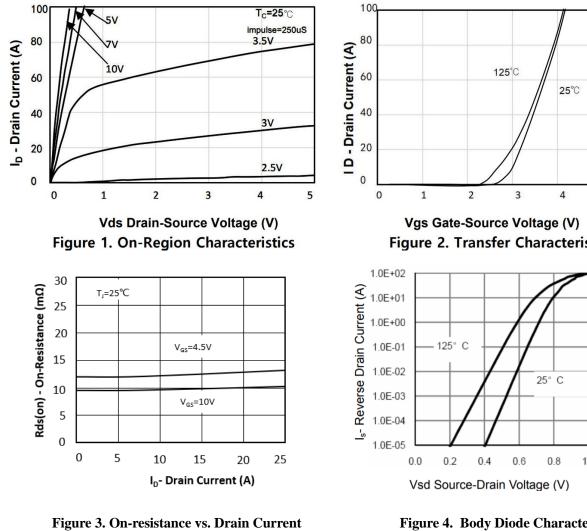

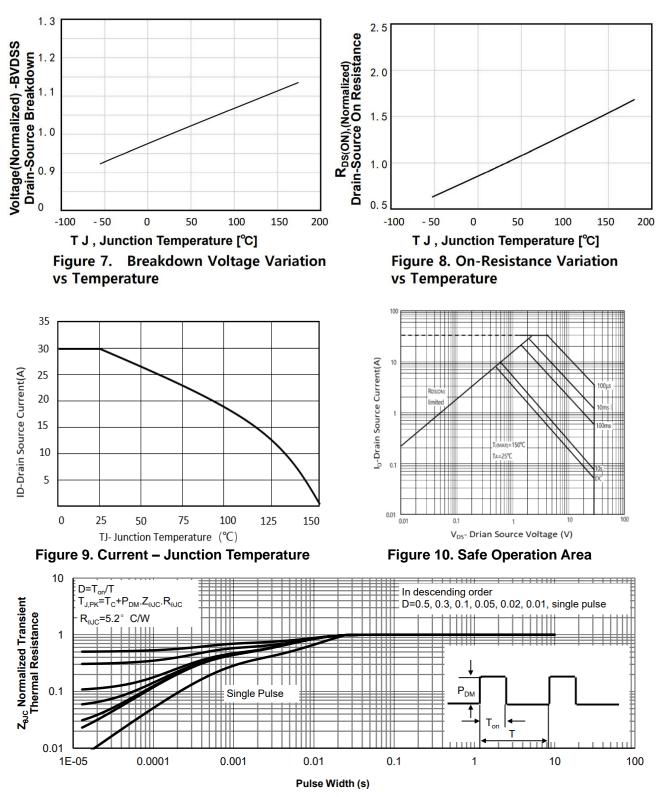

# **Typical Electrical and Thermal Characteristics**

**Figure 5. Gate Charge Characteristics**

5 6 **Figure 2. Transfer Characteristics**

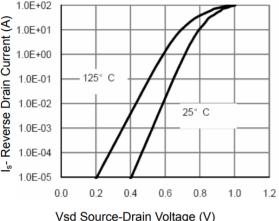

**Figure 4. Body Diode Characteristics**

**Figure 6. Capacitance Characteristics**

LX3030N

Figure 11. Normalized Maximum Transient Thermal Impedance

### Gate Charge Test Circuit & Waveform

### **Resistive Switching Test Circuit & Waveforms**

#### **Unclamped Inductive Switching Test Circuit & Waveforms**

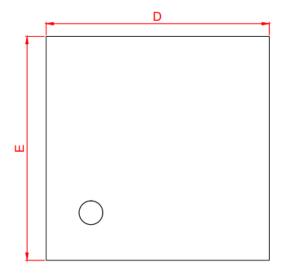

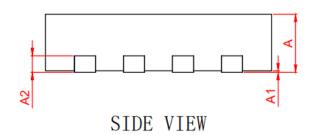

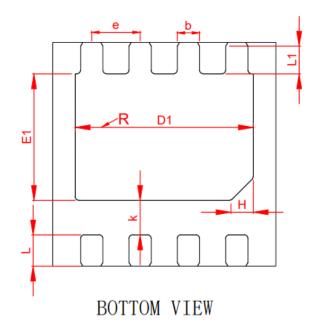

#### **DFN3\*3 Package Information**

|             | MILLIMETER |      |      |

|-------------|------------|------|------|

| SYMBOL      | MIN        | NOM  | MAX  |

| Α           | 0.70       | 0.75 | 0.80 |

| <b>*</b> A1 | 0.00       | 0.02 | 0.05 |

| *b          | 0.27       | 0.32 | 0.37 |

| <b>*</b> A2 | 0.20REF    |      |      |

| * D         | 2.90       | 3.00 | 3.10 |

| * E         | 2.90       | 3.00 | 3.10 |

| *E1         | 1.70       | 1.80 | 1.90 |

| *D1         | 2.35       | 2.45 | 2.55 |

| * e         | 0.65BSC    |      |      |

| *L          | 0.35       | 0.40 | 0.45 |

| h           | 0.30 REF   |      |      |

| * k         | 0.50REF    |      |      |

| *L1         | 0.25       | 0.30 | 0.35 |

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITIAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED.

CHIPLINK DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS.

THIS DOCUMENT SUPERSEDES AND REPLACES ALL INFORMATION PREVIOUSLY SUPPLIED.

CHIPLINK RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.